# HARDWARE REFERENCE MANUAL

# **PMAC PCI Lite**

PCI Format 4-Axis Control Board

400-603657-xHxx

May 19, 2003

Single Source Machine Control

Power // Flexibility // Ease of Use

21314 Lassen Street Chatsworth, CA 91311 // Tel. (818) 998-2095 Fax. (818) 998-7807 // www.deltatau.com

# TABLE OF CONTENTS

| INTRODUCTION                                                                | 1  |

|-----------------------------------------------------------------------------|----|

| Overview                                                                    | 1  |

| Board Configuration                                                         | 1  |

| Base Version                                                                |    |

| Option 2: Dual Ported RAM                                                   |    |

| Option 2B: High-Speed USB Communications Interface                          | 2  |

| Option 5xF: CPU Speed Options                                               |    |

| Option 6: Extended Servo Algorithm Firmware                                 |    |

| Option 6L: Special Lookahead Firmware                                       |    |

| Option 7: Plate Mounting                                                    |    |

| Option 8A: High-Accuracy Clock Crystal                                      |    |

| Option 10: Firmware Version Specification                                   |    |

| Option 12: Analog-to-Digital Converters                                     |    |

| Option 15: V-to-F Converter for Analog Input                                |    |

| Option 16: Battery-Backed Parameter Memory                                  |    |

|                                                                             |    |

| HARDWARE SETUP                                                              |    |

| Power-Supply Configuration Jumpers                                          |    |

| Clock Configuration Jumpers                                                 |    |

| Encoder Configuration Jumpers                                               |    |

| Board Reset/Save Jumpers                                                    |    |

| Communication Jumpers                                                       |    |

| I/O Configuration Jumpers                                                   |    |

| Reserved Configuration Jumpers                                              |    |

| CPU Jumper Configuration                                                    |    |

| Resistor Pack Configuration: Termination Resistors                          |    |

| Resistor Pack Configuration: Differential or Single-Ended Encoder Selection | 9  |

| MACHINE CONNECTIONS                                                         | 11 |

| Mounting                                                                    |    |

| Power Supplies                                                              |    |

| Digital Power Supply                                                        |    |

| Analog Power Supply                                                         |    |

| Overtravel Limits and Home Switches.                                        |    |

| Resistor Pack Configuration: Flag and Digital Inputs Voltage Selection      |    |

| Types of Overtravel Limits                                                  | 12 |

| Home Switches                                                               |    |

| Motor Signals Connections (JMACH Connectors)                                |    |

| Incremental Encoder Connection                                              |    |

| DAC Output Signals                                                          |    |

| Amplifier Enable Signal (AENAx/DIRn)                                        |    |

| Amplifier Fault Signal (FAULTn)                                             |    |

| General-Purpose Digital Inputs and Outputs (JOPTO Port)                     |    |

| Control-Panel Port I/O (JPAN Port).                                         |    |

| Command Inputs                                                              |    |

| Selector Inputs                                                             |    |

| Alternate Use                                                               |    |

| Reset Input                                                                 |    |

| Handwheel Inputs                                                            |    |

| Optional Voltage to Frequency Converter                                     |    |

| Thumbwheel Multiplexer Port (JTHW Port).                                    |    |

| Optional Analog Inputs (JANA Port)                                          |    |

| Compare Equal Outputs Port (JEQU Port)                                      |    |

| Serial Port (JRS422 Port)                                                   |    |

| Machine Connections Example                                                 |    |

| Muchine Connections Example                                                 |    |

| PMAC PCI-LITE SOFTWARE SETUP                                                                 | 22 |

|----------------------------------------------------------------------------------------------|----|

| Communications                                                                               | 22 |

| PMAC I-Variables                                                                             | 22 |

| Operational Frequency and Baud Rate Setup                                                    |    |

| Serial Addressing Card Number                                                                |    |

| Option 16 Supplemental Battery-Backed Memory                                                 | 24 |

| HARDWARE REFERENCE SUMMARY                                                                   | 26 |

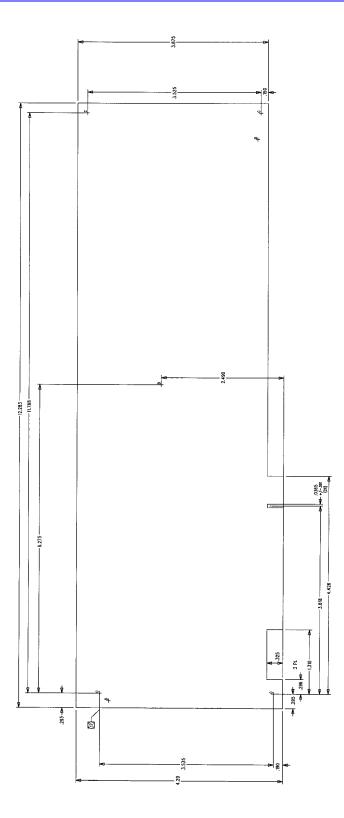

| PMAC PCI-Lite Board Dimensions — Part Number 603657-100                                      |    |

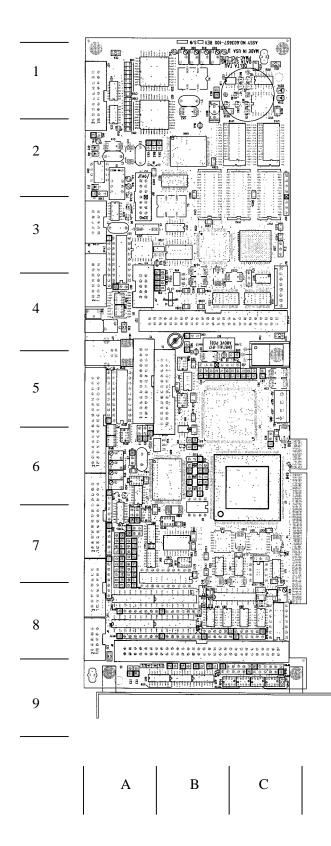

| PMAC PCI-Lite Board Layout. Part Number 603657-10x                                           |    |

| PMAC PCI-Lite Connectors and Indicators                                                      |    |

| J1 - Display Port (JDISP Port)                                                               |    |

| J2 - Control-Panel Port (JPAN Port)                                                          |    |

| J3 - Thumbwheel Multiplexer Port (JTHW Port)                                                 |    |

| J4 - Serial Port (JRS422 Port).                                                              |    |

| J5 - General-Purpose Digital Inputs and Outputs (JOPTO Port)                                 |    |

| J6 – Expansion Port (JXIO Port).                                                             |    |

| J8 - Machine Connectors (JMACH Port)                                                         |    |

| J9 – Compare Equal Outputs Port (JEQU Port)                                                  |    |

| J17 - Serial Port (JRS232 Port)                                                              |    |

| J30 – Optional Analog to Digital Inputs (JANA Port)                                          |    |

| J31 – Optional Universal Serial Bus Port (JUSB Port)                                         |    |

| JS1 – Expansion Ports (JS1 Port)                                                             |    |

| TB1 – Power Supply Terminal Block (JPWR Connector)                                           | 29 |

| LED Indicators                                                                               |    |

| Fuse                                                                                         |    |

| PMAC PCI-LITE E-POINT JUMPER DESCRIPTIONS                                                    | 21 |

| E0: Reserved for Future Use                                                                  |    |

|                                                                                              |    |

| E1 - E2: Machine Output Supply Voltage Configure<br>E3 - E6: Servo Clock Frequency Control   |    |

| E3 - E0: Servo Clock Frequency Control                                                       |    |

| E10A, B, C: Flash Memory Bank Select                                                         |    |

| E17A, B, C. Plash Menory Bank Select<br>E17A-D: Amplifier Enable/Direction Polarity Control  |    |

| E17/A-D. Ampiner Enable/Direction Polarity Control.<br>E18 – E20: Power-Up/Reset Load Source |    |

| E18 – E20. Fower-Op/Reset Load Source                                                        |    |

| E22 - E23: Control Panel Handwheel Enable                                                    |    |

| E22 - E23. Control Failer Handwheer Enable                                                   |    |

| E29 - E33: Phase Clock Frequency Control                                                     |    |

| E34A - E38: Encoder Sampling Clock Frequency Control                                         |    |

| E40 - E43: Clock Direction Control                                                           |    |

| E44 - E47: Serial Port Baud Rate                                                             |    |

| E48: CPU Clock Frequency Control (Option CPU Section)                                        |    |

| E49: Serial Communications Parity Control                                                    |    |

| E50: Flash Save Enable/Disable                                                               |    |

| E51: Normal/Re-Initializing Power-Up                                                         |    |

| E54 - E65: Host Interrupt Signal Select                                                      |    |

| E72 - E73: Panel Analog Time Base Signal Enable                                              |    |

| E74 - E75: Clock Output Control For Ext. Interpolation                                       |    |

| E85: Host-Supplied Analog Power Source Enable                                                |    |

| E87 - E88: Host-Supplied Analog Power Source Enable                                          |    |

| E89: Amplifier-Supplied Switch Pull-Up Enable                                                |    |

| E90: Host-Supplied Switch Pull-Up Enable                                                     |    |

| E98: DAC/ADC Clock Frequency Control                                                         |    |

| E100: Output Flag Supply Select                                                              |    |

| E101 - E102: Motors 1-4 Amplifier Enable Output Configure                                    | 41 |

| E109: Reserved for Future Use                                                                | 41 |

| E110: Serial Port Configure                       |    |

|---------------------------------------------------|----|

| E111: Clock Lines Output Enable                   |    |

| E119: WATCHDOG DISABLE JUMPER                     |    |

| E122: XIN Feature Selection                       |    |

|                                                   | 10 |

| PMAC PCI-LITE MATING CONNECTORS                   |    |

| Base Board Connectors                             |    |

| J1 (JDISP)/Display                                |    |

| J2 (JPAN)/Control Panel                           |    |

| J3 (JTHW)/Multiplexer Port                        |    |

| J4 (JRS422)/RS232 OR 422/Serial Communications    |    |

| J5 (JOPT)/OPTO I/O                                |    |

| J6 (JXIO)/Expansion Board                         |    |

| J8 (JMACH)/Machine Connector                      |    |

| JS1/A-D Inputs 1-4                                |    |

| JEQU/Position Compare                             |    |

| JANA/Analog Inputs Option                         |    |

| PMAC PCI-LITE CONNECTOR PINOUTS                   | 45 |

| J1: Display Port Connector                        |    |

| J2: Control Panel Port Connector                  |    |

| J3: Multiplexer Port Connector                    |    |

| J4: Serial Port Connector                         |    |

| J5: I/O Port Connector                            |    |

| J6: Auxiliary I/O Port Connector                  |    |

| J8: Machine Port Connector                        |    |

| J8: Machine Port Connector                        |    |

| J9 (JEQU): Position-Compare Connector             |    |

| J30 (JANA) Analog Input Port Connector (Optional) |    |

| J31 (JUSB) Universal Serial Bus Port (Optional)   |    |

| JS1: A/D Port 1 Connector                         |    |

| TB1 (JPWR) External Power Supply Connection       |    |

| $\sim$ / / / / / / / / / / / / / / / / / / /      |    |

# INTRODUCTION

## Overview

The PMAC PCI-Lite is a member of the PMAC family of boards optimized for interface to traditional servo drives with single analog inputs representing velocity or torque commands. Its software is capable of eight axes of control, although it can have only four channels of on-board axis interface circuitry.

The PMAC PCI-Lite is a full-sized PCI-bus expansion card. While capable of PCI bus communications, with or without the optional dual-ported RAM, it does not need to be inserted into a PCI expansion slot. Communications can be done through an RS-232 or RS-422 serial port. Standalone operation is possible.

The non-Turbo version of the PMAC PCI-Lite board does not include ICs U140, U143 or U147.

ICs U140, U143 and U147 are not installed in the non-Turbo version of the PMAC Lite-PCI board.

## **Board Configuration**

#### **Base Version**

The base version of the PMAC PCI-Lite provides a 1-1/2-slot board with:

- 40 MHz DSP563xx CPU

- 128k x 24 zero-wait-state flash-backed SRAM

- 512k x 8 flash memory for firmware and user backup

- Latest released firmware version

- RS-232/422 serial interface, PCI bus interface

- Four channels axis interface circuitry, each including:

- 16-bit +/-10V analog output

- 3-channel differential/single-ended encoder input

- Four input flags, two output flags

- Interface to external 16-bit serial ADC

- Display, control panel, mixed I/O, direct I/O interface ports

- Buffered expansion port

- Clock crystal with +/-100 ppm accuracy

- PID/notch/feedforward servo algorithms

- 1-year warranty from date of shipment

- One manuals CD per set of one to four PMACs in shipment (cables, mounting plates, mating connectors not included)

## **Option 2: Dual Ported RAM**

Dual-ported RAM provides a very high-speed communications path for bus communications with the host computer through a bank of shared memory. DPRAM is advised if more than about 100 data items per second are to be passed between the controller and the host computer in either direction.

• Option 2 provides an 8k x 16 bank of on-board dual-ported RAM. The key component on the board is U1.

## **Option 2B: High-Speed USB Communications Interface**

Option 2B provides the high-speed USB communications interface, which is a faster method of communication than the standard RS-232 communications port.

#### **Option 5xF: CPU Speed Options**

The base PMAC PCI-Lite version has a 40 MHz DSP563xx CPU. This is Option 5AF, which is automatically provided if no CPU speed option is specified.

- Option 5AF: 40 MHz DSP563xx CPU (80 MHz 56002 equivalent). This is the default CPU speed.

- Option 5CF: 80 MHz DSP563xx CPU (160 MHz 56002 equivalent).

- Option 5EF: 160 MHz DSP563xx CPU (320 MHz 56002 equivalent).

#### **Option 6: Extended Servo Algorithm Firmware**

• Option 6 provides an Extended (Pole-Placement) Servo Algorithm firmware instead of the regular servo algorithm firmware. This is required only in difficult-to-control systems (resonances, backlash, friction, disturbances, changing dynamics).

#### **Option 6L: Special Lookahead Firmware**

• Option 6L provides a special lookahead firmware for sophisticated acceleration and cornering profile execution. With the lookahead firmware, PMAC automatically controls the speed along the path (but without changing the path) to ensure that axis limits are not violated.

## **Option 7: Plate Mounting**

• Option 7 provides a mounting plate connected to the PMAC with standoffs. It is used to install the PMAC in standalone applications.

#### **Option 8A: High-Accuracy Clock Crystal**

The PMAC PCI-Lite has a clock crystal of nominal frequency 19.6608 MHz (~20 MHz). The standard crystal's accuracy specification is +/-100 ppm.

• Option 8A provides a nominal 19.6608 MHz crystal with a +/-15 ppm accuracy specification.

#### **Option 10: Firmware Version Specification**

Normally the PMAC PCI-Lite is provided with the newest released firmware version. A label on the memory IC shows the firmware version loaded at the factory.

• Option 10 provides for a user-specified firmware version.

#### **Option 12: Analog-to-Digital Converters**

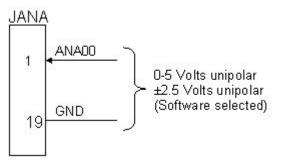

Option 12 permits the installation of 8 or 16 channels of on-board multiplexed analog-to-digital converters. One or two of these converters are read every phase interrupt. The analog inputs are not optically isolated, and each can have a 0 - 5V input range, or a +/-2.5V input range, individually selectable.

- Option 12 provides an 8-channel 12-bit A/D converter. The key components on the board are U20 and connector J30.

- Option 12A provides an additional 8-channel 12-bit A/D converter. The key component on the board is U22.

## **Option 15: V-to-F Converter for Analog Input**

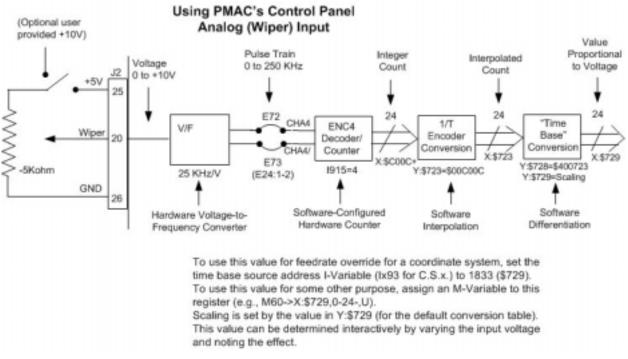

The JPAN control panel port on the PMAC PCI-Lite has an optional analog input called Wiper (because it is often tied to a potentiometer's wiper pin). PMAC PCI-Lite can digitize this signal by passing it through an optional voltage-to-frequency converter, using E-point jumpers to feed this into the Encoder 4 circuitry (no other use is permitted then), and executing frequency calculations using the "time base" feature of the encoder conversion table. The key component on the board is U18.

• Option 15 provides a voltage-to-frequency converter that permits the use of the WIPER input on the control panel port.

#### **Option 16: Battery-Backed Parameter Memory**

The contents of the standard memory are not retained through a power-down or reset unless they have been saved to flash memory first. Option 16 provides supplemental battery-backed RAM for real-time parameter storage that is ideal for holding machine state parameters in case of an unexpected power-down. This memory appears at addresses \$A000 - \$BBFF. The key components on the board are U142, U145, U149, and BT1.

• Option 16A provides a 16k x 24 bank of battery-backed parameter RAM.

# HARDWARE SETUP

On the PMAC, there are many jumpers (pairs of metal prongs), called E-points. Some have been shorted together; others have been left open. These jumpers customize the hardware features of the board for a given application and must be set up appropriately. The following is an overview of the several PMAC jumpers grouped in appropriate categories. For a complete description of the jumper setup configuration, refer to the "PMAC PCI-Lite CPU Board E-Point Descriptions" chapter.

## **Power-Supply Configuration Jumpers**

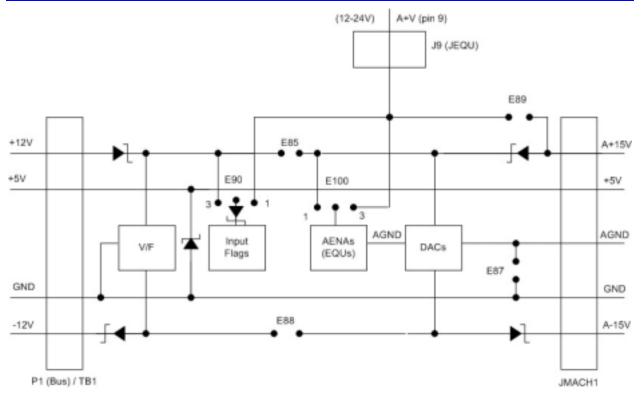

**E85, E87, E88: Analog Circuit Isolation Control** – These jumpers control whether the analog circuitry on the PMAC is isolated from the digital circuitry, or electrically tied to it. In the default configuration, these jumpers are off, keeping the circuits isolated from each other (provided separate isolated supplies are used).

**E89-E90: Input Flag Supply Control** – If E90 connects pins 1 and 2 and E89 is ON, the input flags (+LIMn, -LIMn, HMFLn) are supplied from the analog A+15V supply, which can be isolated from the digital circuitry. If E90 connects pins 1 and 2 and E89 is OFF, the input flags are supplied from a separate A+V supply through pin 9 of the J8 JEQU connector. This supply can be in the +12V to +24V range, and can be kept isolated from the digital circuitry. If E90 connects pins 1 and 2 isolation from the digital circuitry is defeated.

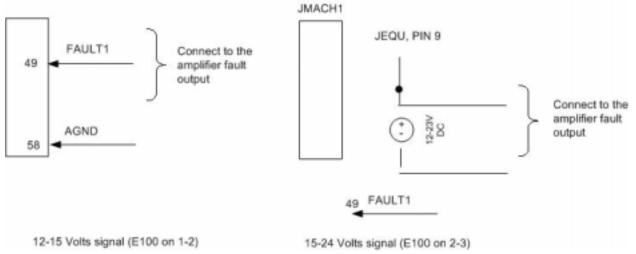

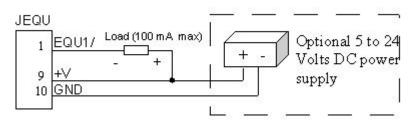

**E100: AENA/EQU Supply Control** – If E100 connects pins 1 and 2, the circuits related to the AENAn, EQUn and FAULTn signals will be supplied from the analog A+15V supply, which can be isolated from the digital circuitry. If E100 connects pins 2 and 3, the circuits will be supplied from a separate A+V supply through pin 9 of the J9 JEQU connector. This supply can be in the +12V to +24V range, and can be kept isolated from the digital circuitry.

## **Clock Configuration Jumpers**

**E3-E6: Servo Clock Frequency Control** –Jumpers E3 – E6 determine the servo-clock frequency by controlling how many times it is divided down from the phase-frequency. The default setting of E3 and E4 OFF, E5 and E6 ON divides the phase-clock frequency by four, creating a 2.25kHz servo-clock frequency. This setting is seldom changed.

**E29-E33: Phase Clock Frequency Control** – Only one of the jumpers E29 – E33, which select the phase-clock frequency, may be on in any configuration. The default setting of E31 ON, which selects a 9kHz phase-clock frequency, is seldom changed.

**E34-E38: Encoder Sample Clock** – Only one of the jumpers E34 – E38, which select the encoder sample clock frequency, may be on in any configuration. The frequency must be high enough to accept the maximum true count rate (no more than one count in any clock period), but a lower frequency can filter out longer noise spikes. The anti-noise digital delay filter can eliminate noise spikes up to one sample-clock cycle wide.

**E40-43:** Servo and Phase Clock Direction Control – Jumpers E40 – E43 determine the direction of the phase and servo clocks: all of these jumpers must be ON for the card to use its internally generated clock signals and to output these on the serial port connector. If any of these jumpers is OFF, the card will expect to input these clock signals from the serial port connector, and its watchdog timer will trip immediately if it does not receive these signals. The card number (0 – 15) for serial addressing of multiple cards on a daisychain serial cable is determined by the PMAC variable I0. See the Software Setup section in this manual for details.

**E48: Option CPU Clock Frequency Control** – If variable I46 is saved at a value greater than 0, I46 will determine the CPU's operational frequency (recommended). For backward compatibility, if I46 is saved at a value of 0, the CPU will operate at 40MHz if E48 is OFF, or at 60MHz if E48 is ON.

**E98: DAC/ADC Clock Frequency Control** – Leave E98 in its default setting of 1-2, which creates a 2.45MHz DCLK signal, unless connecting an ACC-28 A/D-converter board. In this case, move the jumper to connect pins 2 and 3, which creates a 1.22MHz DCLK signal.

## **Encoder Configuration Jumpers**

**Encoder Complementary Line Control** – The selection of the type of encoder used, either single-ended or differential is made through the resistor packs configuration and not through a jumper configuration, as on older PMAC designs.

**E22-E23: Control-Panel Handwheel Enable** – Putting these jumpers ON ties the handwheel-encoder inputs on the JPAN control-panel port to the Channel 2 encoder circuitry. If the handwheel inputs are connected to Channel 2, no encoder should be connected to Channel 2 through the JMACH connector.

**E72-E73: Control Panel Analog Input Enable** – Putting these jumpers ON ties the output of the Option 10 voltage-to-frequency converter that can process the Wiper analog input on the JPAN control panel port to the Channel 4 encoder circuitry. If the frequency signal is connected to Channel 4, no encoder should be connected to Channel 4 through the JMACH connector.

**E74-E75: Encoder Sample Clock Output** – Putting these jumpers ON ties the encoder sample-clock signal to the CHC4 and CHC4/ lines on the JMACH port. This permits the clock signal to be used to synchronize external encoder-processing devices like the ACC-8D Option 8, interpolator board. With these jumpers ON, no encoder input signal should be connected to these pins.

## **Board Reset/Save Jumpers**

**E50:** Flash-Save Enable/Disable Control – If E50 is ON (default), the active software configuration of the PMAC can be stored to non-volatile flash memory with the **SAVE** command. If the jumper on E50 is removed, this **SAVE** function is disabled, and the contents of the flash memory cannot be changed.

**E51: Re-Initialization on Reset Control** – If E51 is OFF (default), PMAC executes a normal reset, loading active memory from the last saved configuration in non-volatile flash memory. If E51 is ON, PMAC re-initializes on reset, loading active memory with the factory default values.

## **Communication Jumpers**

**PCI Bus Base Address Control** – The selection of the base address of the card in the I/O space of the host PC's expansion bus is assigned automatically by the operating system and is not selected through a jumper configuration as ISA bus address would be.

**E44-E47: Serial Baud Rate Selection** – If the saved value of I46 is 0, the CPU's operational frequency is determined by the E48 jumper settings. Then the serial baud rate is determined by a combination of the setting of jumpers E44-E47 and the CPU frequency on a PMAC(1) board. If the CPU's operational frequency has been determined by a non-zero setting of I46, the serial communications baud rate is determined only by variable I54 at power-up/reset. See the Software Setup section of this manual for details.

**E49: Serial Communications Parity Control** – Jump pin 1 to 2 for NO serial parity; remove jumper for ODD serial parity.

**E54-E65: Interrupt Source Control** – These jumpers control which signals are tied to interrupt lines IR5, IR6 and IR7 on PMAC's programmable interrupt controller (PIC) as shown in the interrupt diagram. Only one signal may be tied into each of these lines.

**E110: Serial Port Configure** – Jump pin 1 to 2 for use of the J4 connector as RS-232. Jump pin 2 to 3 for use of the J4 connector as RS-422.

**E111: Clock Lines Output Enable** – Jump pin 1 to 2 to enable the Phase, Servo and Init lines on the J4 connector. Jump pin 2 to 3 to disable the Phase, Servo and Init lines on the J4 connector. For daisychained PMACs sharing the clock lines for synchronization, E111 must be on positions 1 to 2.

## I/O Configuration Jumpers

**E1-E2: Machine Output Supply Configure** – With the default sinking output driver IC (ULN2803A or equivalent) in U13 for the J5 JOPTO port outputs, these jumpers must connect pins 1 and 2 to supply the IC correctly. If this IC is replaced with a sourcing output driver IC (UDN2981A or equivalent), these jumpers must be changed to connect pins 2 and 3 to supply the new IC correctly.

#### Caution

A wrong setting of these jumpers will damage the associated output IC.

**E7: Machine Input Source/Sink Control** – With this jumper connecting pins 1 and 2 (default) the machine input lines on the J5 JOPTO port are pulled up to +5V or the externally provided supply voltage for the port. This configuration is suitable for sinking drivers. If the jumper is changed to connect pins 2 and 3, these lines are pulled down to GND – this configuration is suitable for sourcing drivers.

**E17A - E17D: Motors 1-4 Amplifier-Enable Polarity Control** – Jumpers E17A through E17D control the polarity of the amplifier enable signal for the corresponding motor 1 to 4. When the jumper is ON (default), the amplifier-enable line for the corresponding motor is low true so the enable state is low-voltage output and sinking current, and the disable state is not conducting current. If the default ULN2803A sinking driver used by the PMAC is on U37, this is the fail-safe option. This allows the

circuit to fail in the disable state. With this jumper OFF, the amplifier-enable line is high true so the enable state is not conducting current, and the disable state is low-voltage output and sinking current. (This setting is not generally recommended.)

**E28:** Following-Error/Watchdog-Timer Signal Control – With this jumper connecting pins 2 and 3 (default), the FEFCO/ output on pin 57 of the J8 JMACH servo connector outputs the watchdog timer signal. With this jumper connecting pins 1 and 2, this pin outputs the warning following error status line for the selected coordinate system.

**E101-E102:** Motors 1-4 AENA/EQU voltage configure – The U37 driver IC controls the AENA and EQU signals of motors 1-4. With the default sinking output driver IC (ULN2803A or equivalent) in U37, these jumpers must connect pins 1 and 2 to supply the IC correctly. If this IC is replaced with a sourcing output driver IC (UDN2981A or equivalent), these jumpers must be changed to connect pins 2 and 3 to supply the new IC correctly.

Caution

A wrong setting of these jumpers will damage the associated output IC.

**E122: XIN7 feature selection** – Jump 2-3 to bring the Power Good signal into register XIN7 at Y:\$E801 bit 7.

## **Reserved Configuration Jumpers**

**E0:** Reserved for future use.

**E109:** Reserved for future use.

## **CPU Jumper Configuration**

**E10A-E10C: Flash Memory Bank Select Jumpers** – The flash-memory IC in location U146 on the PMAC PCI-Lite board has the capacity for eight separate banks of firmware, only one of which can be used at any given time. The eight combinations of settings for jumpers E10A, E10B, and E10C select which bank of the flash memory is used. In the factory production process, firmware is loaded only into Bank 0, which is selected by having all of these jumpers OFF.

**E18-E20:** Power-Up State Jumpers – Jumper E18 must be OFF, jumpers E19 and E20 must be ON, in order for the CPU to copy the firmware from flash memory into active RAM on power-up/reset. This is necessary for normal operation of the card. (Other settings are for factory use only.)

**E21: Firmware Load Jumper** – If jumper E21 is ON during power-up/reset, the board comes up in bootstrap mode, which permits the loading of new firmware into the flash-memory IC on the board. When the PMAC Executive program tries to establish communications with a board in this mode, it will automatically detect that the board is in bootstrap mode and ask what file to download as the new firmware. Jumper E21 must be OFF during power-up/reset for the board to come up in normal operational mode.

**E119: Watchdog Timer Jumper** - Jumper E119 must be OFF for the watchdog timer to operate. This is a very important safety feature, so it is vital that this jumper be OFF in normal operation. E1 should only be put ON to debug problems with the watchdog timer circuit.

## **Resistor Pack Configuration: Termination Resistors**

The PMAC provides sockets for termination resistors on differential input pairs coming into the board. There are no resistor packs in these sockets when shipped. If these signals are brought long distances into the PMAC board and ringing at signal transitions is a problem, SIP resistor packs may be mounted in these sockets to reduce or eliminate the ringing. All termination resistor packs have independent resistors (no common connection) with each resistor using two adjacent pins. The following table shows which packs are used to terminate each input device:

| Device    | <b>Resistor Pack</b> | Pack Size |

|-----------|----------------------|-----------|

| Encoder 1 | RP61                 | 6-pin     |

| Encoder 2 | RP63                 | 6-pin     |

| Encoder 3 | RP67                 | 6-pin     |

| Encoder 4 | RP69                 | 6-pin     |

## **Resistor Pack Configuration: Differential or Single-Ended Encoder** Selection

The differential input signal pairs to the PMAC have user-configurable pull-up/pull-down resistor networks to permit the acceptance of either single-ended or differential signals in one setting, or the detection of lost differential signals in another setting.

- The '+' inputs of each differential pair each have a hard-wired 1 k $\Omega$  pull-up resistor to +5V. This cannot be changed.

- The '-' inputs of each differential pair each have a hard-wired 2.2 k $\Omega$  resistor to +5V; also each has another 2.2 k $\Omega$  resistor as part of a socketed resistor pack that can be configured as a pull-up resistor to +5V, or a pull-down resistor to GND.

If this socketed resistor is configured as a pull-down resistor (the default configuration), the combination of pull-up and pull-down resistors on this line acts as a voltage divider, holding the line at +2.5V in the absence of an external signal. This configuration is required for single-ended inputs using the '+' lines alone; it is desirable for unconnected inputs to prevent the pick-up of spurious noise; it is permissible for differential line-driver inputs.

If this socketed resistor is configured as a pull-up resistor (by reversing the SIP pack in the socket), the two parallel 2.2 k $\Omega$  resistors act as a single 1.1 k $\Omega$  pull-up resistor, holding the line at +5V in the absence of an external signal. This configuration is required if encoder-loss detection is desired; it is required if complementary open-collector drivers are used; it is permissible for differential line-driver inputs even without encoder loss detection.

If Pin 1 of the resistor pack (marked by a dot on the pack) matches Pin 1 of the socket (marked by a wide white line on the front side of the board) and a square solder pin on the back side of the board, then the pack is configured as a bank of pull-down resistors. If the pack is reversed in the socket, it is configured as a bank of pull-up resistors.

The following table lists the pull-up/pull-down resistor pack for each input device:

| Device    | <b>Resistor Pack</b> | Pack Size |

|-----------|----------------------|-----------|

| Encoder 1 | RP60                 | 6-pin     |

| Encoder 2 | RP62                 | 6-pin     |

| Encoder 3 | RP66                 | 6-pin     |

| Encoder 4 | RP68                 | 6-pin     |

# **MACHINE CONNECTIONS**

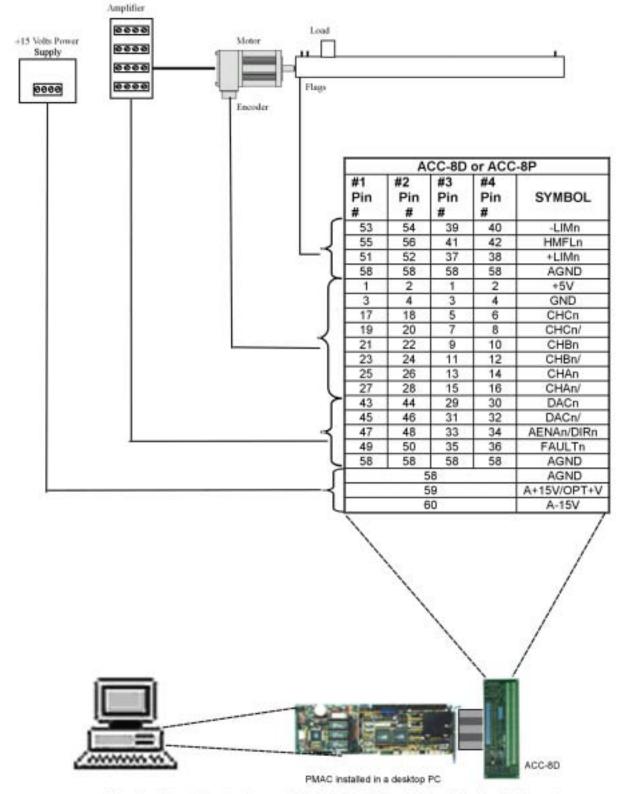

Typically, the user connections are made to a terminal block that is attached to the JMACH connector by a flat cable (Accessory 8D or 8P). The pinout numbers on the terminal block are the same as those on the JMACH connector. The possible choices for breakout boards are:

| Board    | Mounting   | Breakout Style | Breakout<br>Connector | Notes                                      |

|----------|------------|----------------|-----------------------|--------------------------------------------|

| ACC-8P   | DIN – Rail | Monolithic     | Terminal Block        | Simple Phoenix contact board               |

| ACC-8D   | DIN – Rail | Monolithic     | Terminal Block        | Headers for connection to option boards    |

| ACC-8DCE | DIN – Rail | Modular        | D-sub connector       | Fully shielded for easy CE mark compliance |

## Mounting

The PMAC can be mounted in one of two ways: in the PCI bus, or using standoffs.

- PCI bus: To mount in the PCI bus, simply insert the P1 card-edge connector into the PCI socket. If there is a standard PC-style housing, a bracket at the end of the PMAC board can be used to screw into the housing to hold the board down firmly.

- Standoffs: At each of the four corners of the PMAC board, there are mounting holes that can be used to mount the board on standoffs.

## **Power Supplies**

## **Digital Power Supply**

2A @ +5V (+/-5%) (10W) (Eight-channel configuration with a typical load of encoders)

• The host computer provides the 5V power supply if PMAC is installed in its internal bus.

With the board plugged into the bus, it will pull +5V power from the bus automatically and it cannot be disconnected. In this case, there must be no external +5V supply, or the two supplies will fight each other, possibly causing damage. This voltage could be measured between pins 1 and 3 of the terminal block.

• In a stand-alone configuration, when PMAC is not plugged in a computer bus, it will need an external 5V supply to power its digital circuits. The +5V line from the supply should be connected to pin 1 or 2 of the JMACH connector (usually through the terminal block), and the digital ground to pin 3 or 4. ACC-1x provides different options for the 5V power supply.

## **Analog Power Supply**

0.3A @ +12 to +15V (4.5W) 0.25A @ -12 to -15V (3.8W)

The analog output circuitry on PMAC is optically isolated from the digital computation circuitry, and so requires a separate power supply. Bring this in on the JMACH connector. Bring the positive supply (+12 to +15V) in on the A+15V line on pin 59. Bring the negative supply (-12 to -15V) in on the A-15V line on pin 60 and the analog common in on the AGND line on pin 58.

Typically this supply can come from the servo amplifier; many commercial amplifiers provide such a supply, or an external supply may be used. ACC-2x provides different options for the  $\pm$  15V power supply. Even with an external supply, the AGND line should be tied to the amplifier common. It is possible to get the power for the analog circuits from the bus, but doing so defeats optical isolation. In this case, no new connections need to be made. However, be sure jumpers E85, E87, E88, E89, and E90 are set up for this circumstance. (The card is not shipped from the factory in this configuration.)

## **Overtravel Limits and Home Switches**

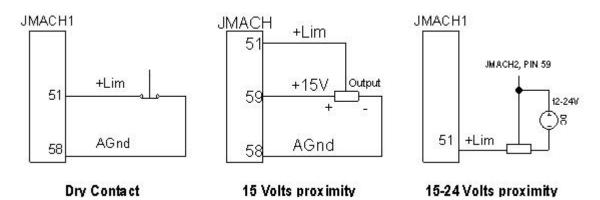

When assigned for the dedicated uses, these signals provide important safety and accuracy functions. +LIMn and -LIMn are direction-sensitive overtravel limits, that must be actively held low (sourcing current from the pins to ground) to permit motion in their direction. The direction sense of +LIMn and -LIMn is as follows: +LIMn should be placed at the negative end of travel, and -LIMn should be placed at the positive end of travel.

## **Resistor Pack Configuration: Flag and Digital Inputs Voltage Selection**

The PMAC is provided with 6-pin sockets for SIP resistor packs for the input flag sets. Each PMAC is shipped without resistor packs installed. If the flag or digital inputs circuits are in the 12V to 15V range, no resistor pack should be installed in these sockets. For flags or digital inputs at 5V levels, quad 1k $\Omega$  SIP resistor packs (1KSIP6C) should be installed in these sockets. The following table lists the voltage selection resistor pack sockets for each input device:

| Device  | Resistor Pack |

|---------|---------------|

| Flags 1 | RP77          |

| Flags 2 | RP83          |

| Flags 3 | RP89          |

| Flags 4 | RP94          |

## **Types of Overtravel Limits**

PMAC expects a closed-to-ground connection for the limits to be considered not on fault. This arrangement provides a failsafe condition and therefore it cannot be reconfigured differently in PMAC.

Usually a passive normally closed switch is used. If a proximity switch is needed instead, use a 15V normally closed to ground NPN sinking type sensor.

Jumper E89, E90 and E100 must be set appropriately for the type of sensor used.

#### **Home Switches**

While normally closed-to-ground switches are required for the overtravel limits inputs, the home switches could be either normally closed or normally open types. The polarity is determined by the home sequence setup, through the I-variables I902, I907, ... I977. However, for the following reasons, the same type of switches used for overtravel limits are recommended:

- Normally closed switches are proven to have greater electrical noise rejection than normally open types.

- Using the same type of switches for every input flag simplifies maintenance stock and replacements.

## Motor Signals Connections (JMACH Connectors)

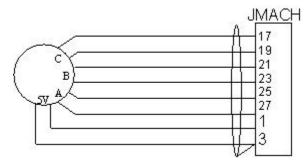

#### **Incremental Encoder Connection**

Each JMACH connector provides two +5V outputs and two logic grounds for powering encoders and other devices. The +5V outputs are on pins 1 and 2; the grounds are on pins 3 and 4. The encoder signal pins are grouped by number: all those numbered 1 (CHA1, CHA1/, CHB1, CHC1, etc.) belong to encoder #1. Usually, the encoder number matches the motor number, but it is not necessary. If the PMAC is not plugged into a bus and drawing its +5V and GND from the bus, use these pins to bring in +5V and GND from the power supply. Connect the A and B (quadrature) encoder channels to the appropriate terminal block pins. For encoder 1, the CHA1 is pin 25, CHB1 is pin 21. If there is a single-ended signal, leave the complementary signal pins floating — do not ground them. However, if single-ended encoders are used, check the settings of the jumpers E18 to E21 and E24 to E27. For a differential encoder, connect the complementary signal lines -- CHA1/ is pin 27, and CHB1/ is pin 23. The third channel (index pulse) is optional; for encoder 1, CHC1 is pin 17, and CHC1/ is pin 19.

**Example:** differential quadrature encoder connected to channel #1:

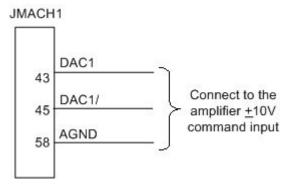

## **DAC Output Signals**

If PMAC is not performing the commutation for the motor, only one analog output channel is required to command the motor. This output channel can be either single-ended or differential, depending on what the amplifier is expecting. For a single-ended command using PMAC channel 1, connect DAC1 (pin 43) to the command input on the amplifier. Connect the amplifier's command signal return line to PMAC's AGND line (pin 58). In this setup, leave the DAC1/ pin floating. Do not ground it.

For a differential command using PMAC channel 1, connect DAC1 (pin 43) to the plus-command input on the amplifier. Connect DAC1/ (pin 45) to the minus-command input on the amplifier. PMAC's AGND should still be connected to the amplifier common. If the amplifier is expecting separate sign and magnitude signals, connect DAC1 (pin 43) to the magnitude input. Connect AENA1/DIR1 (pin 47) to the sign (direction input). Amplifier signal returns should be connected to AGND (pin 58). This format requires some parameter changes on PMAC. (See Ix02 and Ix25.) Jumper E17 controls the polarity of the direction output. This may have to be changed during the polarity test. This magnitude-and-direction mode is suited for driving servo amplifiers that expect this type of input, and for driving voltage-tofrequency (V/F) converters, such as PMAC's ACC-8D Option 2 board, for running stepper motor drivers. If using PMAC to commutate the motor, use two analog output channels for the motor. Each output may be single-ended or differential, just as for the DC motor. The two channels must be consecutively numbered, with the lower-numbered channel having an odd number (e.g., use DAC1 and DAC2 for a motor, or DAC3 and DAC4, but not DAC2 and DAC3, or DAC2 and DAC4). For our motor #1 example, connect DAC1 (pin 43) and DAC2 (pin 45) to the analog inputs of the amplifier. If using the complements as well, connect DAC1/ (pin 45) and DAC2/ (pin 46) the minus-command inputs; otherwise leave the complementary signal outputs floating. To limit the range of each signal to  $\pm$  5V, use parameter Ix69. Any analog output not used for dedicated servo purposes may be utilized as a general-purpose analog output. Usually this is done by defining an M-variable to the digital-to-analog-converter register (suggested M-variable definitions M102, M202, etc.), then writing values to the M-variable. The analog output sare intended to drive high-impedance inputs with no significant current draw. The 220 $\Omega$  output resistors will keep the current draw lower than 50 mA in all cases and prevent damage to the output circuitry, but any current draw above 10 mA can result in noticeable signal distortion.

#### **Example:**

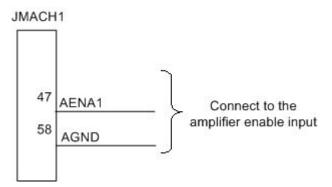

## Amplifier Enable Signal (AENAx/DIRn)

Most amplifiers have an enable/disable input that permits complete shutdown of the amplifier regardless of the voltage of the command signal. PMAC's AENA line is meant for this purpose. If not using a direction and magnitude amplifier or voltage-to-frequency converter, use this pin to enable and disable the amplifier (wired to the enable line). AENA1/DIR1 is pin 47. This signal is an open-collector output with a 3.3 k $\Omega$  pull-up resistor to +V, which is a voltage selected by jumper E100. The pull-up resistor packs are RP43 for channels 1-4. For early tests, this amplifier signal should be under manual control.

This signal could be either sinking or sourcing as determined by chips U37. (See jumpers E100-E102.) For 24V operation, E100 must connect pins 2-3 and a separate power supply must be brought on pins 9-7 of the J9 JEQU connector. The polarity of the signal is controlled by jumpers E17A to E17D. The default is low-true (conducting) enable. Also the amplifier enable signal could be manually controlled by setting Ix00=0 and using the suggested definition of the Mx14 variable.

## **Amplifier Fault Signal (FAULTn)**

This input can take a signal from the amplifier so PMAC knows when the amplifier is having problems, and can shut down action. The polarity is programmable with I-variable Ix25 (I125 for motor #1) and the return signal is analog ground (AGND). FAULT1 is pin 49. With the default setup, this signal must be actively pulled low for a fault condition. In this setup, if nothing is wired into this input, PMAC will consider the motor not to be in a fault condition. The amplifier fault signal could be monitored using the properly defined Mx23 variable.

Some amplifiers share the fault output with the enable\disable status output. In this case a special PLC code must be written with the following sequence:

- Disable the amplifier fault input (see Ix25)

- Enable the motor (J/ command).

- Wait for the amplifier fault input to be false (monitor Mx23).

- Re-enable the amplifier fault input (see Ix25).

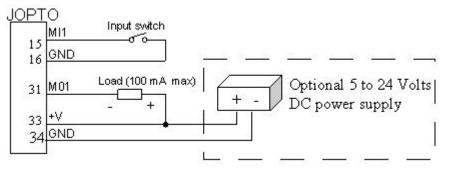

## **General-Purpose Digital Inputs and Outputs (JOPTO Port)**

PMAC's J5 or JOPTO connector provides eight general-purpose digital inputs and eight general-purpose digital outputs. Each input and each output has its own corresponding ground pin in the opposite row. The 34-pin connector was designed for easy interface to OPTO-22 or equivalent optically isolated I/O modules. Delta Tau's Accessory 21F is a six-foot cable for this purpose. Characteristics of the JOPTO port on the PMAC:

- 16 I/O points. 100mA per channel, up to 24V

- Hardware selectable between sinking and sourcing in groups of eight; default is all sinking (inputs can be changed simply by moving a jumper; sourcing outputs must be special-ordered or field-configured)

- Eight inputs, eight outputs only; no changes. Parallel (fast) communications to PMAC CPU

- Not opto-isolated; easily connected to Opto-22 (PB16) or similar modules through ACC-21F cable

Jumper E7 controls the configuration of the eight inputs. If it connects pins 1 and 2 (the default setting), the inputs are biased to +5V for the OFF state, and they must be pulled low for the ON state. If E7 connects pins 2 and 3, the inputs are biased to ground for the OFF state, and must be pulled high for the ON state. In either case, a high voltage is interpreted as a 0 by the PMAC software, and a low voltage is interpreted as a 1.

#### Caution

Do not connect these outputs directly to the supply voltage, or damage to the PMAC will result from excessive current draw.

Having Jumpers E1 and E2 set wrong can damage the IC. The +V output on this connector has a 2A fuse, F1, for excessive current protection.

PMAC is shipped standard with a ULN2803A sinking (open-collector) output IC for the eight outputs. These outputs can sink up to 100mA and have an internal 3.3 k $\Omega$  pull-up resistor to go high (RP18). A high-side voltage (+5 to +24V) may be provided to pin 33 of the JOPTO connector, and allow this to pull up the outputs by connecting pins 1 and 2 of jumper E1. Also, jumper E2 must connect pins 1 and 2 for a ULN2803A sinking output.

It is possible for these outputs to be sourcing drivers by substituting a UDN2981A IC for the ULN2803A. This U13 IC is socketed, and so may be replaced easily. For this driver, the internal resistor packs pull-down instead. With a UDN2981A driver IC, Jumper E1 must connect pins 2 and 3, and Jumper E2 must connect pins 2 and 3.

The outputs can be configured individually to a different output voltage by removing the internal pull-up resistor pack RP18 and connecting a separate external pull-up resistor to the desired voltage level to each output.

Example: Standard configuration using the ULN2803A sinking (open-collector) output IC

## **Control-Panel Port I/O (JPAN Port)**

The J2 (JPAN) connector is a 26-pin connector with dedicated control inputs, dedicated indicator outputs, a quadrature encoder input, and an analog input. The control inputs are low-true with internal pull-up resistors. They have predefined functions unless the control-panel-disable I-variable (I2) has been set to 1. If this is the case, they may be used as general-purpose inputs by assigning M-variable to their corresponding memory-map locations (bits of Y address \$FFC0).

#### **Command Inputs**

JOG-/, JOG+/, PREJ/ (return to pre-jog position), and HOME/ affect the motor selected by the FDPn/ lines (see below). The ones that affect a coordinate system are STRT/ (run), STEP/, STOP/ (abort), and HOLD/ (feed hold) affect the coordinate system selected by the FDPn/ lines.

#### Caution

It is not a good idea to change the selector inputs while holding one of the jog inputs low, for releasing the jog input will not stop the previously selected motor. This can lead to a dangerous situation.

#### **Selector Inputs**

The four low-true BCD-coded input lines FDP0/ (LSBit), FDP1/, FDP2/, and FDP3/ (MSBit) form a low-true BCD-coded nibble that selects the active motor and coordinate system (simultaneously). Usually, these are controlled from a single 4-bit motor/coordinate-system selector switch. The motor selected with these input lines will respond to the motor-specific inputs. It will also have its position following function turned on (Ix06 is set to 1 automatically.); the motor just de-selected has its position following function turned off (Ix06 is set to 0 automatically.).

#### **Alternate Use**

If I2 has been set to 1, the discrete inputs can be used for parallel-data servo feedback or master position. The ACC-39 Handwheel Encoder Interface board provides 8-bit parallel counter data from a quadrature encoder to these inputs. Refer to the ACC-39 manual and Parallel Position Feedback Conversion section in the Setting Up A Motor chapter for more details.

#### **Reset Input**

Input INIT/ (reset) affects the entire card. It has the same effect as cycling power or a host \$\$\$ command. It is hard-wired, so it retains its function even if I2 is set to 1.

#### **Handwheel Inputs**

The handwheel inputs HWCA and HWCB can be connected to the second encoder counter on PMAC with jumpers E22 and E23. If these jumpers are ON, nothing else should be connected to the Encoder 2 inputs. The signal can be interpreted either as quadrature or as pulse (HWCA) and direction (HWCB), depending on the value of I905. I905 also controls the direction sense of this input. Make sure that the Encoder 2 jumper E26 is set for single ended signals, connecting pins 1 and 2.

#### **Optional Voltage to Frequency Converter**

The Wiper analog input (0 to +10V on PMAC referenced to digital ground) provides an input to a voltage-to-frequency converter (V/F) with a gain of 25kHz/V, providing a range of 0-250kHz. The output of the V/F can be connected to the Encoder 4 counter using jumpers E72 and E73. If these jumpers are ON, nothing else should be connected to the Encoder 4 inputs. Make sure that the Encoder 4 jumper E24 is set for single-ended signals, connecting pins 1 and 2. This feature requires Option15.

#### **Frequency Decode**

When used in this fashion, set up Encoder 4 for pulse-and-direction decode by setting I915 to 0 or 4. A value of 4 is usually used, because with CHB4 (direction) unconnected, a positive voltage causes the counter to count up. The encoder conversion table can then take the difference in the counter each servo cycle and scale it, providing a value proportional to frequency, and therefore to the input voltage. Usually this is used for feedrate override (time base control), but the resulting value can be used for any purpose. The resulting value in the default setup can be found at X:\$729,24.

#### **Power Supply**

For the V/F converter to work, PMAC must have +/-12V supply referenced to digital ground. If PMAC is in a bus configuration, usually this comes through the bus connector from the bus power supply. In a standalone configuration, this supply must be brought through the bus connector (or the supply terminal block), or it must be jumpered over from the analog side with E85, E87, and E88, defeating the optical isolation on the board.

## Thumbwheel Multiplexer Port (JTHW Port)

The Thumbwheel Multiplexer Port, or Multiplexer Port, on the JTHW (J3) connector has eight input lines and eight output lines. The output lines can be used to multiplex large numbers of inputs and outputs on the port, and Delta Tau provides accessory boards and software structures (special M-variable definitions) to capitalize on this feature. Up to 32 of the multiplexed I/O boards may be daisychained on the port, in any combination.

- The ACC-18 Thumbwheel Multiplexer board provides up to 16 BCD thumbwheel digits or 64 discrete TTL inputs per board. The TWD and TWB forms of M-variables are used for this board.

- The ACC-34x family Serial I/O Multiplexer boards provide 64 I/O point per board, optically isolated from PMAC. The TWS form of M-variables is used for these boards.

- The ACC-8D Option 7 Resolver-to-Digital Converter board provides up to four resolver channels whose absolute positions can be read through the thumbwheel port. The TWR form of M-variables is used for this board.

- The ACC-8D Option 9 Yaskawa<sup>TM</sup> Absolute Encoder Interface board can connect to up to four of these encoders. The absolute position is read serially through the multiplexer port on power up.

If none of these accessory boards is used, the inputs and outputs on this port may be used as discrete, nonmultiplexed I/O. They map into PMAC's processor space at Y address \$FFC1. The suggested Mvariable definitions for this use are M40 to M47 for the eight outputs, and M50 to M57 for the eight inputs. The ACC-27 Optically Isolated I/O board buffers the I/O in this non-multiplexed form, with each point rated to 24V and 100mA.

## **Optional Analog Inputs (JANA Port)**

The JANA port is present only if Option 12 is ordered for the PMAC. Option 12 provides eight 12-bit analog inputs (ANAI00-ANAI07). Option 12A provides eight additional 12-bit analog inputs (ANA08-ANAI15) for a total of 16 inputs. The analog inputs can be used as unipolar inputs in the 0V to +5V range, or bi-polar inputs in the -2.5V to +2.5V range.

The analog-to-digital converters on PMAC require +5V and -12V supplies. These supplies are not isolated from digital +5V circuitry on PMAC. If the PMAC is plugged into the PCI bus, the supplies are taken from the bus power supply. In a standalone application, the supplies must be brought in on terminal block TB1. The -12V and matching +12V supply voltages are available on the J30 connector to supply the analog circuitry providing the signals.

Only one pair of analog-to-digital converter registers is available to the PMAC processor at any given time. The data appears to the processor at address Y:FFC8. The data from the selected analog input 0 to 7 (ANAI00-ANAI07) appears in the low 12 bits; the data from the selected analog input 8 to 15 (ANAI08-ANAI15) appears in the high 12 bits (this data is present only if Option 12A has been ordered). The input is selected and the conversion is started by writing to this same word address Y:FFC8. A value of 0 to 7 written into the low 12 bits selects the analog input channel of that number (ANAI00-ANAI07) to be converted in unipolar mode (0V to +5V). A value of 0 to 7 written into the high 12 bits or the high 12 bits is eight higher (8 to 15), the same input channel is selected, but the conversion is in bipolar mode (-2.5V to +2.5V).

PMAC variables I60 and I61 allow an automatic conversion of the analog inputs. Setting I60=\$FFC8 and I61 with the number of converted registers desired minus one, the converted data can be found in registers \$0708 to \$070F. See the PMAC Software Reference manual for further details.

## **Compare Equal Outputs Port (JEQU Port)**

The compare-equals (EQU) outputs have a dedicated use of providing a signal edge when an encoder position reaches a pre-loaded value. This is very useful for scanning and measurement applications. Instructions for use of these outputs are presented in the PMAC's User Manual.

Outputs can be configured sinking or sourcing by replacing the chips U37 and configuring the jumpers E101-102. The voltage levels can be individually configured by removing resistor pack RP43 and connecting an external pull-up resistor in each output to the desired voltage level.

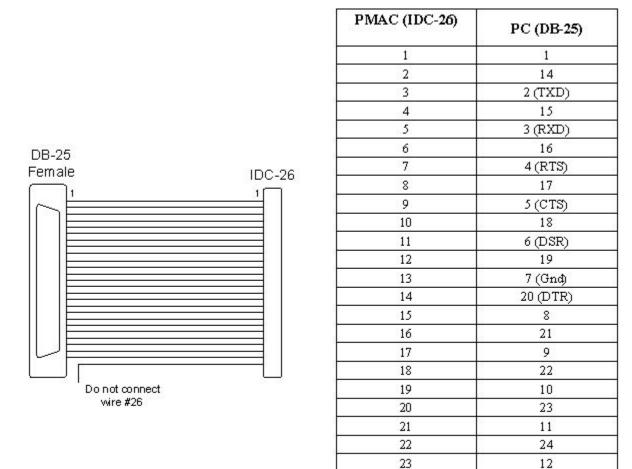

## Serial Port (JRS422 Port)

For serial communications, use a serial cable to connect the PC's COM port to the PMAC's J4 serial port connector. Delta Tau provides the Accessory 3D cable to connect the PMAC-PCI to a DB-25 connector. Standard DB-9-to-DB-25 or DB-25-to-DB-9 adapters may be needed for a particular setup. Jumper E110 selects between RS-232 and RS422 signal types for the J4 connector. If a cable needs to be made, use a flat cable prepared with flat-cable type connectors as indicated in the following diagram:

24

25

26

25

13

No connect

## **Machine Connections Example**

Note: For this configuration, jumpers E85, E87, E88, E89, and E90 are left at the default settings

# **PMAC PCI-LITE SOFTWARE SETUP**

Note

The PMAC PCI-Lite requires the use of V1.17 or newer firmware. There are few differences between the previous V1.16H firmware and the V1.17 firmware other than the addition of internal support for the Flex CPU design.

## **Communications**

Delta Tau provides communication tools that take advantage of the PCI bus Plug & Play feature of 32bits Windows<sup>®</sup> based computers. With PEWIN32 Pro, a PMAC PCI-Lite board plugged in a PCI bus slot will be recognized by the operating system when the computer is booted up. The available PCI address, Dual Ported RAM address and Interrupt lines are set automatically by the operating system and can be checked (but not modified) in the resources page of the device manager.

## **PMAC I-Variables**

PMAC has a large set of Initialization parameters (I-variables) that determine the personality of the card for a specific application. Many of these are used to configure a motor properly. Once set up, these variables may be stored in non-volatile EAROM memory (using the **SAVE** command) so the card is always configured properly (PMAC loads the EAROM I-variable values into RAM on power-up).

The easiest way to program, set up and troubleshoot PMAC is by using the PMAC Executive Program PEWIN and its related add-on packages P1Setup and PMACPlot. These software packages are available by ordering the ACC-9WN accessory.

The programming features and configuration variables for the PMAC are fully described in the PMAC User and Software manuals.

## **Operational Frequency and Baud Rate Setup**

Note

Older PMAC boards required a start-up PLC for setting the operational frequency at 80 MHz. That method is not compatible with the PMAC PCI-Lite board and will shut down the board when used.

The operational frequency of the CPU is set in software by the PMAC I46 I- variable. If this variable is set to 0, PMAC firmware looks at the jumper E48 to set the operational frequency. If I46 is set to a value greater than 0, the operational frequency is set to 10MHz \* (I46 + 1), regardless of the jumper setting. If the desired operational frequency is higher than the maximum rated frequency for that CPU, the operational frequency will be reduced to the rated maximum. It is always possible to operate the Flex CPU board at a frequency below its rated maximum. I46 is used only at power-up/reset. To change the operational frequency, set a new value of I46, issue a **SAVE** command to store this value in non-volatile flash memory. Then issue a **\$\$\$\$** command to reset the controller.

To determine the frequency at which the CPU is actually operating, issue the **TYPE** command to the PMAC. The PMAC will respond with five data items, the last of which is CLK Xn, in which n is the multiplication factor from the 20MHz crystal frequency (not 10MHz). n should be equivalent to (I46+1)/2 if I46 is not requesting a frequency greater than the maximum rated for that CPU board. n will be 2 for 40MHz operation, 4 for 80MHz operation, and 8 for 160MHz operation.

If the CPU's operational frequency has been determined by (a non-zero setting of) I46, the serial communications baud rate is determined at power-up/reset by variable I54 alone according to the following table:

| I54                                                         | Baud Rate | I54 | Baud Rate |  |

|-------------------------------------------------------------|-----------|-----|-----------|--|

| 0                                                           | 600       | 8   | 9600      |  |

| 1                                                           | 900       | 9   | 14,400    |  |

| 2                                                           | 1200      | 10  | 19,200    |  |

| 3                                                           | 1800      | 11  | 28,800    |  |

| 4                                                           | 2400      | 12  | 38,400    |  |

| 5                                                           | 3600      | 13  | 57,600    |  |

| 6                                                           | 4800      | 14  | 76,800    |  |

| 7                                                           | 7200      | 15  | 115,200*  |  |

| * The CPU must be run at an exact multiple of 30MHz in      |           |     |           |  |

| order to use 115,200 baud serial communications. Otherwise, |           |     |           |  |

| the baud rate will not be exact enough to ensure proper     |           |     |           |  |

| communications.                                             |           |     |           |  |

The card number (0 - 15) for serial addressing of multiple cards on a daisychain serial cable is determined by variable I0. Jumpers E40 – E43 determine the direction of the phase and servo clocks. All of these jumpers must be ON for the card to use its internally generated clock signals and to output these on the serial port connector. If any of these jumpers is OFF, the card will expect to input these clock signals from the serial port connector, and its watchdog timer will trip immediately if it does not receive these signals.

## **Serial Addressing Card Number**

I0 controls the card number for software addressing purposes on a multi-drop serial communications cable. If I2 is set to 2, the PMAC must be addressed with the @n command where n matches the value of I0 on the board, before it will respond. If the PMAC receives the @n command where n does not match I0 on the board, it will stop responding to commands on the serial port. No two boards on the same serial cable may have the same value of I0.

If the @@ command is sent over the serial port, all boards on the cable will respond to action commands. However, only the board with I0 set to 0 will respond to the host with handshake characters and/or data responses. All boards on the cable will respond to control-character action commands such as  $\langle CTRL-R \rangle$ , regardless of the current addressing.

#### Note

RS-422 serial interfaces must be used on all PMAC boards for multi-drop serial communications. This will not work with RS-232 interfaces. Typically, multiple PMAC boards on the same serial cable will share servo and phase clock signals over the serial port cable for tight synchronization. If the servo and phase clock lines are connected between multiple PMACs, only one of the PMAC boards can be set up to output these clocks (E40 – E43 all ON for a PMAC PCI-Lite). All of the other boards in the chain must be set up to input these clocks (one or more of the jumpers E40 – E43 OFF for a PMAC PCI-Lite).

Any PMAC PCI-Lite board with one or more of E40 - E43 OFF is expecting its Servo and Phase clock signals externally from a Card 0. If it does not receive these clock signals, the watchdog timer will immediately shut down the board and the red LED will light.

If the PMAC PCI-Lite is set to receive external Servo and Phase clock signals for synchronization purposes, but is not using multi-drop serial communications, I0 does not need to be changed from 0.

To set up a board to communicate as Card 1 to Card 15 on a multi-drop serial cable, first communicate with the board as Card 0. Set I0 to specify the card number (software address) that the board will have on the multi-drop cable. Also, set I1 to 2 to enable the serial software addressing. Store these values to the non-volatile flash memory with the **SAVE** command. Then turn off power. If the board is to input its clocks, remove any of the E40-E43 jumpers. Connect the multi-drop cable. Restore power to the system.

## **Option 16 Supplemental Battery-Backed Memory**

If Option 16 supplemental battery-backed parameter memory is ordered, an extra bank of memory with battery backup circuitry is provided. This option can be ordered only if the main memory is flash backed (Option 4A, 5A, 5B, or 5C). This memory is for user parameter storage only. From PMAC programs it can be accessed with M-variables only (L-variables also in compiled PLCs). The on-line direct-memory read and write commands can be used from the host computer as well.

With M-variable access, arrays can be created with indirect addressing techniques by pointing a second M-variable to the definition of a first M-variable that points into this memory area. For example, with the M-variable definitions:

```

M0->L:$A000 ; 1st long word of Opt. 16 RAM; floating point

M10->Y:$BC000,0,16 ; Low 16 bits of M0 def., with pointer address

```

The following code segment could load a sine table into the first 360 words of the Option 16 RAM:

```

P1=0

WHILE (P1<360)

M10=$A000+P1 ; Sets address that M0 points to

M0=SIN(P1) ; Puts value in register that M0 points to

P1=P1+1

ENDWHILE</pre>

```

#### Note

This technique is not possible with L-variables in compiled PLCs. But it is possible with M-variables in compiled PLCs.

Physically, the Option 16 memory is a 16k x 24 bank of battery-backed static RAM. It maps into the PMAC and PMAC2 at addresses \$A000 to \$BFFF, on both the X and Y data buses, an 8k x 48 block of address space. Addresses Y:\$BC00 to Y:\$BFFF are double-mapped with the main flash-backed RAM for the M-variable definitions, and should not be used for user parameter storage.

Any value written into the Option 16 memory will be retained automatically through a power-down or reset; no **SAVE** operation is required. The power draw on the battery is low enough that typically battery life will be limited only by the quoted 10-year life of the battery.

# HARDWARE REFERENCE SUMMARY

## PMAC PCI-Lite Board Dimensions — Part Number 603657-100

| Feature | Location | Feature | Location |  |

|---------|----------|---------|----------|--|

| E0      | A6       | E55     | B7       |  |

| E1      | A6       | E57     | B7       |  |

| E2      | A6       | E58     | B7       |  |

| E3      | A8       | E59     | B7       |  |

| E4      | A8       | E61     | B7<br>B7 |  |

| E5      | A7       | E62     | B7       |  |

| E6      | A7       | E63     | B6       |  |

| E7      | A6       | E65     | B6       |  |

| E10A    | A2       | E72     | A9       |  |

| E10B    | A2       | E73     | A9       |  |

| E10C    | B2       | E74     | A9       |  |

| E17A    | A8       | E75     | B9       |  |

| E17B    | A8       | E85     | B5       |  |

| E17C    | A8       | E87     | C5       |  |

| E17D    | A7       | E88     | A2       |  |

| E18     | B4       | E89     | B5       |  |

| E19     | B4       | E90     | B5       |  |

| E20     | B4       | E98     | A4       |  |

| E21     | B4       | E100    | A3       |  |

| E22     | A9       | E101    | A7       |  |

| E23     | A9       | E102    | A7       |  |

| E28     | C6       | E109    | B6       |  |

| E29     | A8       | E110    | A7       |  |

| E30     | A8       | E111    | A7       |  |

| E31     | A8       | E119    | B6       |  |

| E32     | A8       | E122    | B6       |  |

| E33     | A8       | D15     | A3       |  |

| E34     | A8       | D20     | A2       |  |

| E34A    | A8       | D20A    | C1       |  |

| E35     | A8       | D21     | A2       |  |

| E36     | A8       | D21A    | C1       |  |

| E37     | A8       | F1      | A4       |  |

| E38     | A8       | J1      | A4       |  |

| E40     | B5       | J2      | A5       |  |

| E41     | B5       | J3      | B5       |  |

| E42     | B5       | J4      | A7       |  |

| E43     | B5       | J5      | A5       |  |

| E44     | B5       | J6      | A9       |  |

| E45     | B5       | J8      | B9       |  |

| E46     | C5       | J9      | A3       |  |

| E47     | C5       | J17     | A4       |  |

| E48     | C5       | J30     | A1       |  |

| E49     | C5       | J31     | A5       |  |

| E50     | C5       | JS1     | A8       |  |

| E51     | B6       | TB1     | C6       |  |

## **PMAC PCI-Lite Connectors and Indicators**

## J1 - Display Port (JDISP Port)

The JDISP connector allows connection of the ACC-12 or ACC-12A liquid crystal displays, or of the ACC-12C vacuum fluorescent display. Both text and variable values may be shown on these displays through the use of the **DISPLAY** command, executing in either motion or PLC programs.

## J2 - Control-Panel Port (JPAN Port)

The JPAN connector is a 26-pin connector with dedicated control inputs, dedicated indicator outputs, a quadrature encoder input, and an analog input (requires PMAC Option 15). The control inputs are low true with internal pull-up resistors. They have predefined functions unless the control-panel-disable I-variable (I2) has been set to 1. If this is the case, they may be used as general-purpose inputs by assigning M-variable to their corresponding memory-map locations (bits of Y address \$FFC0).

#### J3 - Thumbwheel Multiplexer Port (JTHW Port)

The Thumbwheel Multiplexer Port, or Multiplexer Port, on the JTHW connector has eight input lines and eight output lines. The output lines can be used to multiplex large numbers of inputs and outputs on the port, and Delta Tau provides accessory boards and software structures (special M-variable definitions) to capitalize on this feature. Up to 32 of the multiplexed I/O boards may be daisychained on the port, in any combination.

## J4 - Serial Port (JRS422 Port)

For serial communications, use a serial cable to connect the PC's COM port to the PMAC's serial port connector. Delta Tau provides the accessory 3D cable for this purpose, which connects PMAC to a DB-25 connector. Standard DB-9-to-DB-25 or DB-25-to-DB-9 adapters may be needed for a particular setup.

## J5 - General-Purpose Digital Inputs and Outputs (JOPTO Port)

PMAC's JOPTO connector provides eight general-purpose digital inputs and eight general-purpose digital outputs. Each input and each output has its own corresponding ground pin in the opposite row. The 34-pin connector was designed for easy interface to OPTO-22 or equivalent optically isolated I/O modules. Delta Tau's Accessory 21F is a six-foot cable for this purpose.

## J6 – Expansion Port (JXIO Port)

This port is used only when connecting to optional PMAC accessory boards.

#### J8 - Machine Connectors (JMACH Port)

The primary machine interface connector is JMACH, labeled J8 on the PMAC. It contains the pins for four channels of machine I/O: analog outputs, incremental encoder inputs, and associated input and output flags, plus power-supply connections.

## J9 – Compare Equal Outputs Port (JEQU Port)

The compare-equals (EQU) outputs have a dedicated use of providing a signal edge when an encoder position reaches a pre-loaded value. This is useful for scanning and measurement applications. Instructions for use of these outputs are presented in the PMAC's User Manual.

## J17 - Serial Port (JRS232 Port)

This connector applies only to the turbo version of the PMAC PCI-Lite board. It allows PMAC to communicate through its auxiliary RS-232 serial port.

#### J30 – Optional Analog to Digital Inputs (JANA Port)

This optional port is used to bring in the analog signals for the optional analog to digital inputs set. This feature provides up to 16 analog inputs in the range of 0 to 5V unipolar or  $\pm 2.5V$  bipolar.

## J31 – Optional Universal Serial Bus Port (JUSB Port)

This optional port allows communication with PMAC through a standard USB connection.

#### JS1 – Expansion Ports (JS1 Port)

This port is used only when connecting to optional PMAC accessory boards.

#### **TB1 – Power Supply Terminal Block (JPWR Connector)**

This terminal block may be used as an alternative power supply connector if PMAC is not installed in a PCI-bus.

#### **LED Indicators**

**D20 and D20A:** when these green LEDs are lit, they indicate that power is applied to the +5V input.

**D21 and D21A:** when these red LEDs are lit, they indicate that the watchdog timer has tripped and shut down the PMAC.

**D15:** The PMAC has an interlock circuit that drops out the  $\pm 15V$  supplies to the analog outputs through a fail-safe relay if any supply on PMAC is lost. In this case the green LED D15 will be off.

#### **Fuse**

The 5V output through the J5 JOPTO connector is protected by F1, which is a 2-Amp fuse of the following type:

Manufacturer: LittleFuse

Part Number: 021-273002-004

# **PMAC PCI-LITE E-POINT JUMPER DESCRIPTIONS**

## **E0: Reserved for Future Use**

| E Point &<br>Physical Layout | Location | Description     | Default   |

|------------------------------|----------|-----------------|-----------|

| E0<br>1<br>2                 | A6       | For future use. | No jumper |

# E1 - E2: Machine Output Supply Voltage Configure

| E Point &       | Location                                                                  | Description                                                                                                     | Default                 |

|-----------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------|

| Physical Layout |                                                                           |                                                                                                                 |                         |

| E1              | E1 A6 Jump pin 1<br>24V) to pin<br>ULN2803A<br>configuratio<br>outputs M0 |                                                                                                                 | 1-2 Jumper<br>installed |

|                 |                                                                           | Caution                                                                                                         |                         |

|                 |                                                                           | The jumper setting must match the type of driver IC, or damage to the IC will result.                           |                         |

|                 |                                                                           | Jump pin 2 to 3 to apply GND to pin<br>10 of U13 (should be UDN2981A for<br>source output configuration).       |                         |

| E2<br>123       | A6                                                                        | Jump pin 1 to 2 to apply GND to pin<br>10 of U13 (should be ULN2803A for<br>sink output configuration).         | 1-2 Jumper<br>installed |

|                 |                                                                           | Caution                                                                                                         |                         |

|                 |                                                                           | The jumper setting must match the type of driver IC, or damage to the IC will result.                           |                         |

|                 |                                                                           | Jump pin 2 to 3 to apply +V (+5V to 24V) to pin 10 of U13 (should be UDN2981A for source output configuration). |                         |

### E3 - E6: Servo Clock Frequency Control